삼성 파운드리, '1.4나노·패키징'으로 '2030신화' 도전 TSMC와의 '나노경쟁'에서 우위 지키고 이종결합 기술 선점

김혜란 기자공개 2022-10-06 11:24:00

이 기사는 2022년 10월 05일 07:36 thebell 에 표출된 기사입니다.

삼성전자 파운드리(반도체 위탁생산)가 초미세공정과 최첨단 패키징 기술을 선점해 현재 세계 1위 파운드리 대만 TSMC를 압도하겠다는 비전을 제시했다. TSMC와 시장점유율 격차가 40%포인트 가까이 나는 상황에서 판을 뒤집을 승부수가 '초격차 기술'에 있다는 판단에서다.TSMC보다 먼저 1.4나노미터(㎚·1㎚는 10억분의 1m) 공정을 도입하고 첨단 적층 패키징 기술을 개발해 고객사를 유인하겠다는 전략을 공개했다.

◇3나노→2나노→1.4나노 선점, TSMC 압도한다

3일(현지시간) 최시영 삼성전자 파운드리사업부 사장은 미국 실리콘밸리에서 열린 '삼성파운드리 포럼'에서 "2025년에 2나노, 2027년에 1.4나노 공정을 도입하겠다"며 "최 사장도 포럼에서 "공정 혁신과 동시에 2.5차원(2.5D), 3D 이종 집적(Heterogeneous Integration) 패키징 기술 개발도 가속화할 것"이라고 발표했다.

TSMC와 인텔 등 글로벌 파운드리 중 1.4나노 공정 타임라인을 밝힌 건 삼성전자가 처음이다. TSMC도 1.4나노 공정 개발에 착수한 것으로 알려졌지만 지금까지 구체적인 양산 일정을 제시한 적은 없다.

파운드리에서 공정 미세화가 중요한 건 회로 폭이 좁아지면 칩 크기를 줄일 수 있고, 무엇보다 소비전력이 줄고 속도는 빨라지기 때문이다. 또 한 웨이퍼에서 더 많은 칩을 생산할 수 있어 제조 원가 절감에도 유리하다.

삼성전자가 1.4나노 공정 도입 일정을 경쟁사보다 먼저 내놓을 수 있었던 데는 올해 세계 최초로 3나노 양산을 시작한 자신감이 바탕에 있는 것으로 보인다. 삼성전자 파운드리는 지난 6월 게이트올어라운드(GAA) 기반 3나노 제품 양산에 성공하며 기술 경쟁력을 증명해 보였다.

다만 TSMC와의 '나노경쟁'은 한 번의 승부수로 끝날 싸움은 아니다. 양산은 삼성전자가 먼저 시작했으나 뒤따라온 TSMC가 3나노 제품 공급사로 애플을 유치했다. 삼성전자가 1나노대 공정 기술에 먼저 도달하겠다는 강한 의지를 보인 것도 TSMC와의 경쟁에서 밀리지 않기 위해서다.

파운드리 공정 기술력을 이야기할 때 미세화만큼이나 중요한 분야가 첨단 패키징이다.

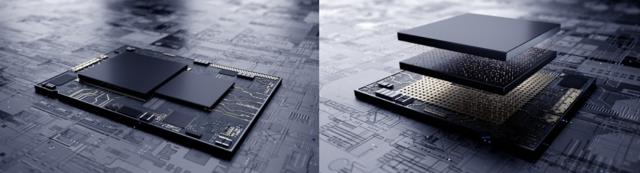

앞으로 미래 파운드리의 경쟁력은 적층 기술 개발·상용화가 얼마나 잘 이뤄졌느냐가 결정한다. 첨단 패키징 기술의 진화 방향성은 분명하다. 다른 칩을 하나의 반도체처럼 이어 붙이거나 쌓아 올리는 이종결합, 3D 패키징, 칩렛(Chiplet), SiP(System in Package) 등이다.

현존 기술로는 메모리와 비메모리라는 종류가 다른 칩은 한 칩처럼 쌓을 수가 없다. 그런데 이것이 가능해지면 메모리와 로직(시스템) 반도체 간 신호 연결이 더 빠르게 이뤄져 속도와 전력효율을 높일 수 있다. 이는 패키징 작업을 담당하는 후공정(OSAT)와 파운드리가 내재화해 구현해야 하는 기술이다.

2.5D는 실리콘 관통 전극(TSV) 기술을 활용해 메모리는 적층하되 로직 칩은 메모리 위에 쌓지 않고 병렬로 배치한 뒤 한 칩으로 패키징한다. 여기에서 더 발전한 3D는 여러 종류의 반도체 칩을 위로 쌓아 하나의 칩처럼 결합하는 기술이다.

삼성전자는 2018년 'I-큐브'(2.5D), 2020년 'X-큐브'(3D) 등의 패키징 적층 기술을 내놨으며, TSMC도 자체 3D 패키징 기술인 'SoIC'(System on Integrated Chip)을 내세우고 있다. 삼성전자 측은 "u-Bump(micro Bump)형 X-Cube를 2024년에 양산하고, 2026년에는 Bump-less형 X-Cube를 선보일 계획"이라고 설명했다. X-큐브 기술 고도화로 적층 패키징에서도 TSMC보다 매력적인 기술 경쟁력으로 무장하겠다는 전략이 읽힌다.

'u-Bump(micro Bump)'는 일반 범프 대비 더 많은 입출력(I/O) 단자를 패키징에 넣을 수 있어 더 많은 데이터 처리가 가능하며 'Bump-less'는 패키징에서 범프를 없애고 더 많은 I/O를 삽입해 데이터의 처리 양을 더 많이 구현할 수 있다는 게 삼성 측 설명이다.

< 저작권자 ⓒ 자본시장 미디어 'thebell', 무단 전재, 재배포 및 AI학습 이용 금지 >

best clicks

최신뉴스 in 인더스트리

-

- '3D 세포 관찰' 토모큐브의 상장 재도전, 예심 신청

- 율호,정부 핵심광물 공급망 확대 지원 선정

- 김연수 한컴 대표, '탁월한 선구안' AI 빅테크 이끈다

- CBI 관계사 지비이노베이션, 쌍전광산 장비설비 구축

- 오가노이드사이언스, 기평 신청…사업성 입증 '관건'

- 대동, 농업 챗GPT 서비스 'AI대동이' 오픈

- 자사주 전량 소각 감성코퍼레이션 "ESG 경영 시작"

- [교육업체 생존전략 돋보기]교원, 교육 매출 1조 탈환 전략 '대규모 투자'

- 라온시큐어, 아시아·태평양 '디지털 ID 톱 벤더' 선정

- '자사주 매입' 대동전자, 자진상폐 노리나

김혜란 기자의 다른 기사 보기

-

- 자사주 전량 소각 감성코퍼레이션 "ESG 경영 시작"

- 오픈엣지테크놀로지, 자율주행 겨냥 고성능 NPU IP 출시

- [이사회모니터]레이저쎌, 앰코 출신 장효성 부사장 영입

- 경남제약, 인후염 완화 '리놀에스트로키' 허니·자몽맛 출시

- [K-배터리 밸류업 리포트]덕산일렉테라 모기업 덕산테코피아, 신사업 '본궤도'

- [thebell note]씨아이에스의 가지 않은 길

- [Red & Blue]'MS 협약' 샌즈랩, '애저' 인프라 활용 기대감

- [Company Watch]'다나와·에누리' 커넥트웨이브, 데이터커머스 약진

- 경남제약, 레모나 젤리 '샤인머스캣·블루베리맛' 출시

- [Red & Blue]에프에스티, 극자외선 펠리클 기대감 '반짝'